Digital System Design Using Fsms: A Practical Learning Approach » książka

topmenu

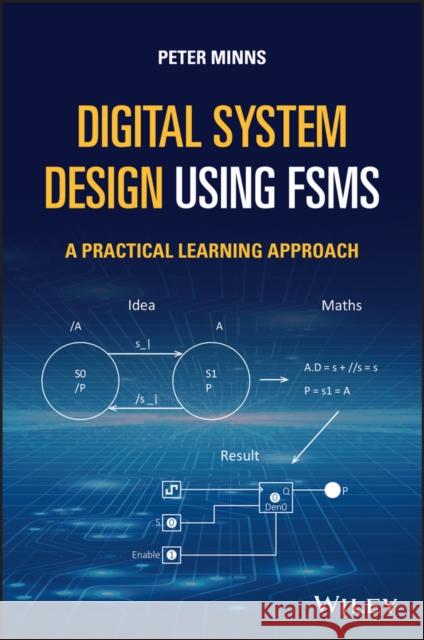

Digital System Design Using Fsms: A Practical Learning Approach

ISBN-13: 9781119782704 / Angielski / Twarda / 2021 / 352 str.

Kategorie:

Kategorie BISAC:

Wydawca:

John Wiley and Sons Ltd

Język:

Angielski

ISBN-13:

9781119782704

Rok wydania:

2021

Ilość stron:

352

Waga:

0.76 kg

Wymiary:

24.41 x 16.99 x 2.06

Oprawa:

Twarda

Wolumenów:

01

Dodatkowe informacje:

Bibliografia